|

||||

|

|

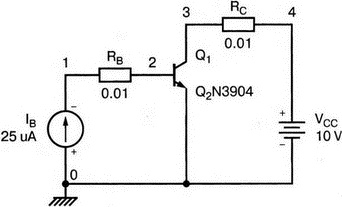

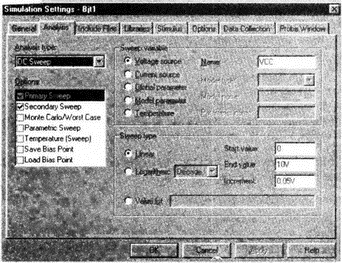

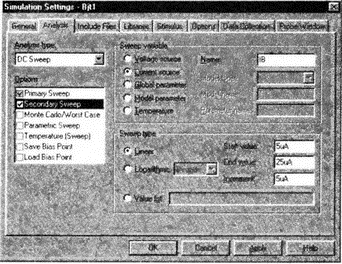

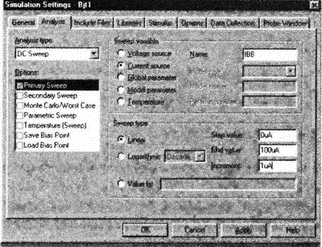

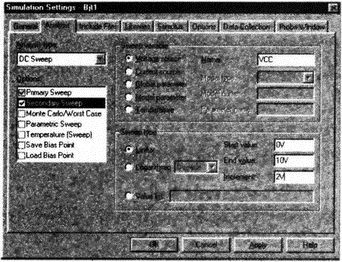

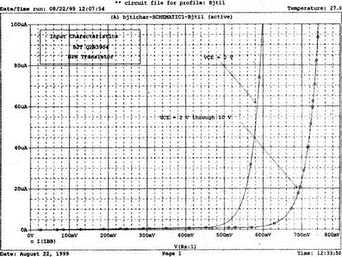

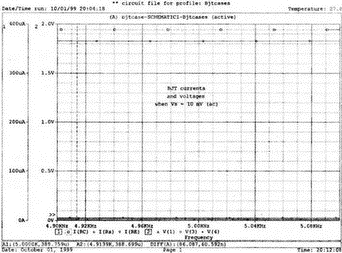

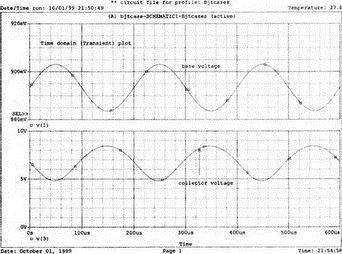

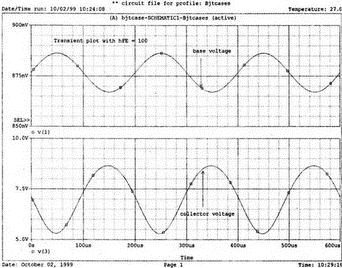

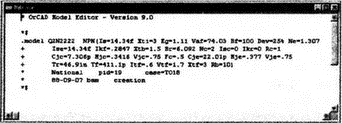

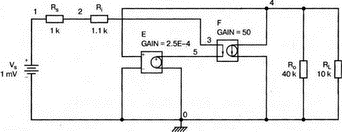

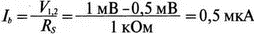

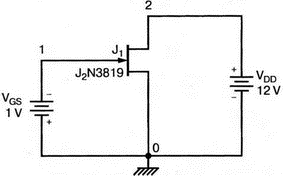

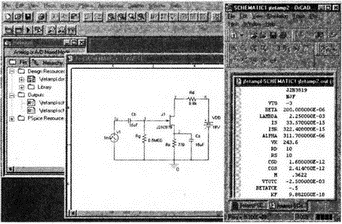

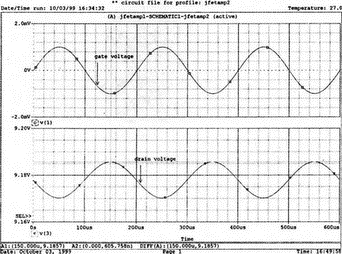

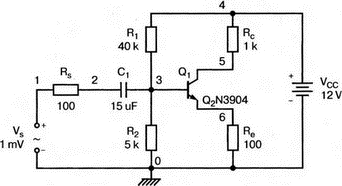

15. Транзисторные цепи в CaptureВ главе 10 исследовалась модель PSpice для биполярного транзистора (BJT). В демонстрационной версии PSpice имеется шесть транзисторов BJT (Q2N2222, Q2N2907A, Q2N3904, Q2N3906, Q2N6052 и Q2N6059), три из которых npn-, а три других — pnp-транзисторы. Чтобы показать некоторые из свойств этих компонентов, начнем с примера, использующего Q2N3904. Выходные характеристики Q2N3904Для получения выходных характеристик вернемся к схеме на рис. 10.1. Создайте новый проект в Capture с именем bjtchar. Введем компонент IDC, затем R (для RB), затем снова R (для RC), затем VDC и 0 для «земли». Затем выберем транзистор типа Q2N3904 из библиотеки eval. Установим имена и значения компонентов, соответствующие рисунку, и соединим компоненты проводами. Пронумеруйте узлы, как на рис. 10.1 (с помощью Place, Netlist). Небольшое замечание касается условного направления тока через RС. Ниже приведена команда PSpice для ввода резистора RС. RC 4 3 0.01 Порядок следования узлов (4, 3) означает, что ток резистора будет положителен, когда он направлен справа налево, то есть от узла 4 к узлу 3. Применим это соглашение к нашему анализу в Capture. Выберите RС и дважды поверните появившееся изображение, чтобы привести направление в соответствие с порядком следования узлов. Схема показана на рис. 15.1.  Рис. 15.1. Схема для биполярного транзистора, полученная в Capture Для моделирования используйте имя Bjt1 и выберите тип анализа DC Sweep. Команда для анализа на PSpice: .dc VCC 0 10V 0.05V IB 5uA 25uA 5uA используется, чтобы выполнить вложенную вариацию. В Capture, для внутреннего цикла выбирается в качестве переменной напряжение источника VCC, которое линейно изменяется от 0 до 10 В с шагом 0,05 В, как показано на рис. 15.2. Переменной внешнего цикла является ток IB, изменяющийся от 5 до 25 мкА с шагом 5 мкА (рис. 15.3).  Рис. 15.2. Установки для моделирования биполярного транзистора  Рис. 15.3. Использование источника тока для внешнего цикла вариации параметров Выполните моделирование и в Probe получите график I(RC). При этом будет выведено необходимое семейство характеристик, с одной кривой для каждого приращения тока базы в 5 мкА. Результаты показаны на рис. 15.4.  Рис. 15.4. Выходные характеристики биполярного транзистора Выходной файл, полученный в Capture, показан на рис. 15.5. Сравните его с соответствующим выходным файлом, приведенным в главе 10. Отметим две команды, приведенные под заголовком Analysis directives: и порядок следования узлов для строки, вводящей RC: R RC 4 3 0.01 **** 09/27/99 14:13:33 *********** Evaluation PSpice (Nov 1998) ********** ** circuit file for profile: Bjt1 *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .DC LIN V_VCC 0 10V 0.05V + LIN I_IB 5uA 25uA 5uA .PROBE *Netlist File: .INC "bjtchar-SCHEMATIC1.net" *Alias File: **** INCLUDING bjtchar-SCHEMATIC1.net **** * source BJTCHAR V_VCC 4 0 10V R_RC 4 3 0.01 R_RB 12 0.01 I_IB 0 1 DC 25uA Q_Q1 3 2 0 Q2N3904 **** RESUMING bjtchar-SCHEMATIC1-Bjt1.sim.cir **** .INC "bjtchar-SCHEMATIC1.als" **** INCLUDING bjtchar-SCHEMATIC1.als **** .ALIASES V_VCC VCC(+=4 -=0 ) R_RC RC(1=4 2=3 ) R_RB RB(1=1 2=2 ) I_IB IB(+=0 -=1 ) Q_Q1 Q1(c=3 b=2 e=0 ) _ _(1=1) _ _(2=2) _ _(3=3) _ _(4=4) .ENDALIASES **** BJT MODEL PARAMETERS Q2N3904 NPN IS 6.734000E-15 BF 416.4 Рис. 15.5. Выходной файл для биполярного транзистора Такой порядок был определен, когда мы дважды повернули RC из первоначальной позиции. Транзистор введен строкой Q_Q1 3 2 0 Q2N3904 Полюса 3, 2, 0 соответствуют коллектору, базе и эмиттеру. Входные характеристики Q2N3904Используем схему, показанную на рис. 10.3, чтобы получить входные характеристики транзистора Q2N3904. После создания нового проекта bjtichar разместим компоненты обычным способом. Резистор RS необходимо трижды повернуть, резистор RL вращать не нужно. Пронумеруйте узлы, как показано на рис. 15.6, и сохраните проект. Для моделирования используйте вариацию dc sweep с именем Bjti1 с внутренним циклом вариации по току источника IВВ в линейном диапазоне от 0 до 100 мкА и с шагом в 1 мкА. На рис. 15.7 показана вкладка для установки опций этой вариации. В качестве параметра внешнего цикла вариации выбирается напряжение источника VCC от 0 до 10 В с шагом в 2 В (рис. 15.8). Выполните моделирование и в Probe установите в качестве переменной по оси X напряжение на узле 1 (напряжение на базе) V(Rs:I). График I(BB) отображает ток базы. Все кривые этого семейства, кроме первой (при VCE=0), сливаются в одну (рис. 15.9). Выходной файл показан на рис. 15.10 для сравнения с предыдущим выходным файлом.  Рис. 15.6. Цепи смещения для биполярного транзистора  Рис. 15.7. Установка опций при снятии входных характеристик  Рис. 15.8. Установка опций для внешнего цикла вариации  Рис. 15.9. Входные характеристики биполярного транзистора **** 09/27/99 14:13:33 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Bjt1 *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .DC LIN V VCC 0 10V 0.05V + LIN I_IB 5uA 25uA 5uA .PROBE *Netlist File: .INC "bjtchar-SCHEMATIC1.net" *Alias File: **** INCLUDING bjtchar-SCHEMATIC1.net **** * source BJTCHAR V_VCC 4 0 10V R_RC 4 3 0.01 R_RB 1 2 0.01 I_IB 0 1 DC 25uA Q_Q1 3 2 0 Q2N3904 **** INCLUDING bjtchar-SCHEMATIC1.als **** .ALIASES V VCC VCC(+=4 -=0 ) R_RC RC(1=4 2=3 ) R_RB RB(1=1 2=2 ) I_IB IB(+=0 -=1 ) Q_Q1 Q1(c=3 b=2 e=0 ) _ _(1=1) _ _(2=2) _ _(4=4) _ _(3=3) .ENDALIASES .END **** BJT MODEL PARAMETERS Q2N3904 NPN IS 6.734000E-15 BF 416.4 Рис. 15.10. Выходной файл для выходных характеристик биполярного транзистора Изучение схем с общим эмиттером на биполярных транзисторахДля изучения цепей смещения в главе 10 была использована схема на рис. 10.7. Соберите эту схему в Capture, создав новый проект Bjtcase. Напомним, что необходимо трижды повернуть резисторы, чтобы первый полюс каждого резистора оказался наверху. Значения будут такими же, как на рис. 10.7: R1=40 кОм, R2=3,3 кОм, Rc=4,7 кОм, RE=220 кОм и VCC=12 В. Транзистор 2N2222 обозначен в библиотеке eval как Q2N2222. Пронумеруйте узлы, как на рис. 10.7, затем сохраните полученный рисунок (рис. 15.11). Чтобы получить анализ цепей смещения, используйте моделирование на PSpice под именем Bjtcase. Выберите тип анализа Bias Point и для Output File Option установите опцию "Include detailed bias point information (.OP)". Выполните моделирование, проверьте ошибки, исследуйте выходной файл, затем отредактируйте его в Word и распечатайте. Сравните ваши результаты с показанными на рис. 15.12. Значения параметров смещения должны совпадать с приведенными в главе 10.  Рис. 15.11. Схема для определения точки покоя усилителя ОЭ на биполярном транзисторе **** 10/01/99 11:14:59 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Bjtcases *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .CP .PROBE *Netlist File: .INC "bjtease-SCHEMATIC1.net" * Alias File: **** INCLUDING bjtcase-SCHEMATIC1.net **** * source BJTCASE Q_Q1 3 14 Q2N2222 V_VCC 20 12V R_RE 4 0 220 R_RC 2 3 4.7k R_R2 10 3.3k R_R1 2 1 40k **** RESUMING bjtcase-SCHEMATIC1-Bjtcases.sim.cir **** .INC "bjtcase-SCHEMATIC1.als" **** INCLUDING bjtcase-SCHEMATIC1.als **** .ALIASES Q_Q1 Q1(c=3 b=1 e=4 ) V_VCC VCC(+=2 -=0 ) R_RE RE(1=4 2=0 ) R_RC RC(1=2 2=3 ) R_R2 R2(1=1 2=0 ) R_R1 R1(1=2 2=1 ) _ _(1=1) _ _(2=2) _ _(3=3) _ _(4=4) .ENDALIASES .END **** BJT MODEL PARAMETERS Q2N2222 NPN IS 14.340000E-15 BF 255.9 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) .8933 ( 2) 12.0000 ( 3) 6.7651 ( 4) .2466 VOLTAGE SOURCE CURRENTS NAME CURRENT V_VCC -1.391E-03 TOTAL POWER DISSIPATION 1.67E-02 WATTS Рис. 15.12. Выходной файл для усилителя ОЭ на биполярном транзисторе Обратите внимание, что мы не вывели значения токов через резисторы, как делали это на рис. 10.8, поскольку директива .PRINT DC не доступна в Capture. Таким образом, дополнительная работа, необходимая для анализа в Capture, не оправдана, если нас интересуют только параметры смещения. Для проведения анализа переменных составляющих используем созданную нами схему, просто добавив недостающие компоненты. Анализ на переменном токеДополним рисунок предыдущего примера, который был назван bjtcase (откройте его опять в случае необходимости). Добавим компоненты, как показано на рис. 10.9, преобразовав его в усилитель ОЭ, выходное напряжение которого снимается с коллектора. Если необходимо, переместите существующую схему в правую часть рисунка, чтобы иметь больше места для размещения дополнительных компонентов и полей около них. Для этого выделите всю схему, затем, поместив курсор внутри выделенного участка, перетащите схему в нужное место. Добавьте источник Vs (используйте компонент VAC), Rs=50 Ом, Сb=15 мкФ и Се=15 мкФ. Пронумеруйте новые узлы согласно рис. 15.13. Вместо анализа параметров смещения используйте вариацию по переменному току (ас sweep).  Рис. 15.13. Схема усилителя ОЭ на биполярном транзисторе Из главного меню PSpice выберите Edit Simulation Settings и затем анализ AC Sweep/Noise в диапазоне от 4900 до 5100 Гц для 201 точки. Обратите внимание, что на рис. 10.10 анализ был проведен для частоты f=5 кГц, но чтобы получить напряжение и ток в Probe, мы должны вместо одной частоты использовать диапазон частот. Проведите анализ и получите графики I(RC), I(Rs) и I(RE). Используйте режим курсора, чтобы проверить эти значения при f=5 кГц: I(RC)=388 мкА, I(Rs)=5,52 мкА и I(RE)=3,77 мкА. Теперь введите дополнительную ось Y и получите графики V(1), V(3) и V(4). Снова с помощью курсора убедитесь, что V(1)=9,72 мВ, V(3)=1,827 В и V(4)=829,9 мкВ при f=5 кГц. График из Probe показан на рис. 15.14 с током I(RC)=388 мкА при f=5 кГц. Перемещение курсора от одного графика к другому легко осуществить с помощью комбинации клавиш [Ctrl]+[>]. Запишите значения каждого тока и напряжения, которые появляются на табло Probe Cursor.  Рис. 15.14. Токи и напряжения биполярного транзистора в схеме на рис. 15.13 Анализ переходных процессовПри продолжении анализа переменных составляющих на рис. 10.9 рассмотрим временные диаграммы напряжений на базе и коллекторе, которые были показаны на рис. 10.11. Для этого необходимо провести анализ переходных процессов вместо вариации на переменном токе, при этом компонент типа VAC, представляющий входное напряжение Vs, должен быть заменен на компонент VSIN. Задайте величину Vs так, чтобы амплитуда его составляла 10 мВ, но мы будем считать это значение действующим для упрощения анализа. Сделайте эту замену на рисунке, затем отредактируйте параметры настройки моделирования для анализа переходных процессов. Выполните анализ переходных процессов для интервала в 0,6 мс, как в главе 10, используя шаг в 0,6 мкс. В Probe получите на одном экране графики напряжения на коллекторе V(3) и напряжения на базе V(1) (как в главе 10). Сравните ваши результаты с рис. 10.11. Амплитуда напряжения на базе равна 9,72 мВ, амплитуда напряжения на коллекторе составляет 1,807 В, коэффициент усиления по напряжению с базы на коллектор, таким образом, равен 186. Как показано на рис. 15.15, уровень постоянной составляющей выходного напряжения равен 6,756 В; входного составляет 0,893 В, эти значения соответствуют показанным в результатах анализа смещения.  Рис. 15.15. Временные диаграммы для напряжений на базе и на коллекторе транзистора в схеме с ОЭ на биполярном транзисторе Изменение параметров транзистораТранзистор Q2N2222 использовался в предыдущих примерах как типичный элемент, применяемый в реальных схемах. Если вы работаете в лаборатории с транзистором, коэффициент усиления которого hFE значительно меньше, можно изменить схему, чтобы получить результаты, более соответствующие вашим ожиданиям. Продолжите работу с рисунком bjtcase, снова открыв проект в случае необходимости. Выберите Q2N2222, затем Edit, PSpice Model. Появится окно, показывающее «Bjtcase-OrCAD Model Editor — [Q2N2222]». Слева вы увидите идентифицированный транзистор, а справа — список различных параметров, используемых в модели транзистора. Просмотрите в приложении Е полный список этих параметров. Замените Bf=255,9 на новое значение Bf=100, более соответствующее фактическому значению для транзистора, который вы используете в лаборатории. Это окно показано на рис. 15.16. Чтобы сохранить это изменение, используйте File, Close. Когда появится вопрос, хотите ли вы сохранить изменения для Bjtcase, нажмите Yes. Затем, выбрав Save as, вы можете сохранить имя файла Bjtcase. После этого выберите File, Exit и выполните моделирование снова.  Рис. 15.16. Редактирование модели PSpice в окне Model Editor Чтобы выполнить анализ переходных процессов, просто выберите PSpice, Run и получите желательные результаты. В Probe получите графики напряжения на коллекторе V(3) и на базе V(1), и отметьте изменения в их уровнях по сравнению с предыдущим анализом. В качестве упражнения найдите размах колебаний (двойную амплитуду) для каждого напряжения, которые должны составлять v(3)=3,35 В и v(1)=19,3 мВ, что соответствует коэффициенту усиления по напряжению Av=174. Обратите внимание, что коэффициент усиления ненамного меньше, чем в случае, когда BF=255,9. Графики показаны на рис. 15.17.  Рис. 15.17. Временные диаграммы для входного и выходного напряжений при hFE = 100 **** 10/02/99 10:11:05 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Bjtcases *Libraries: * Local Libraries : .LIB *.\bjtcase.lib" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .TRAN 0 0.6ms 0 0.6us .PROBE *Netlist File: .INC "bjtcase-SCHEMATIC1.net" * Alias File: **** INCLUDING bjtcase-SCHEMATIC1.net **** * source BJTCASE Q_Q1 3 1 4 Q2N2222 V_VCC 2 0 12V R_RE 4 0 220 R_RC 2 3 4.7k R_R2 10 3.3k R_R1 2 1 40k R_ Rs 1A 1B 50 C_Cb 1B 1 15uF С_Ce 4 0 15uF V_Vs 1A 0 +SIN 0 10mV 5kHz 0 0 0 **** RESUMING bjtcase-schematic1-bjtcases.sim.cir **** .INC "bjtcase-SCHEMATIC1.als" **** INCLUDING bjtcase-SCHEMATIC1.als **** *.ALIASES Q_Q1 Q1(c=3 b=1 e=4 ) V_VCC VCC(+=2 -=0 ) R_RE RE(1=4 2=0 ) R_RC RC(1=2 2=3 ) R_R2 R2(1=1 2=0 ) R=R1 R1(1=2 2=1 ) R_Rs Rs(1=1A 2=1B ) С_Cb Cb(1=1B 2=1 ) C_Ce Ce(1=4 2=0 ) V_Vs Vs(+=1A -=0 ) .ENDALIASES **** RESUMING bjtcase-schematic1-bjtcases.sim.cir **** .END Unable to find index file bjtease.ind for library file bjtcase.lib Making new index file bjtcase.ind for library file bjtcase.lib Index has 1 entries from 1 file(s). ** circuit file for profile: Вjtcases **** BJT MODEL PARAMETERS Q2N2222 NPN IS 14.340000E-15 BF 100 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) .8768 ( 2) 12.0000 ( 3) 7.1059 ( 4) .2318 ( 1A) 0.0000 ( 1B) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_VCC -1.319E-03 V_Vs 0.000E+00 TOTAL POWER DISSIPATION 1.58E-02 WATTS Рис. 15.18. Выходной файл при hFE = 100 Выходной файл для схемы с измененным параметром транзистора показан на рис. 15.18. Обратите внимание на новое значение BF=100, которое мы изменили перед выполнением анализа. Также обратите внимание на раздел в выходном файле, содержащий инструкции: Unable to find index file bjtcase.ind for library file bjtcase.lib Making new index file bjtcase.ind for library file bjtcase.lib Index has 1 entries from 1 file(s). Это означает, что изменение в параметрах не могло бы быть найдено из предыдущего анализа и что был создан новый индексный файл для новой библиотеки bjtcase.lib. Индексный файл не является текстовым, но bjtcase.lib может быть просмотрен при двойном щелчке на нем или же открыт в Notepad. В PSpice этот файл выглядит, как на рис. 15.19. Если вы хотите просмотреть всю типовую библиотеку устройств eval.lib, ищите ее в C:\Program Files\OrCAD Demo\Capture\library\PSpice  Рис. 15.19. Индексный файл при BF = 100 Когда вы найдете файл eval.lib, дважды щелкните на нем и программа OrCAD будет загружена с листингом всех имеющихся в библиотеке устройств.[9] Он должен быть подобен листингу, показанному в приложении Е. Использование моделей с h-параметрамиВ главе 3 h-параметры для транзистора использовались, чтобы показать, как академическая модель для биполярного транзистора (BJT) обрабатывается в PSpice. В модели были использованы два зависимых источника Е и F. Когда эта схема получена в Capture, ее едва можно узнать, так как Е и F показаны как два четырехполюсника с входными полюсами слева и выходными справа. На рис. 3.7 усилитель ОЭ показан при входном сигнале в 1 мВ. Хотя на схеме был показан входной источник переменного напряжения, было указано, что мы могли бы обмануть PSpice, получив полезную информацию при анализе на постоянном токе (для точки покоя) и интерпретировав затем результаты для переменного тока. Это экономит время и усилия, если схема не содержит реактивных элементов. Мы можем теперь создать схему в Capture, дав этому проекту имя hparmod и использовав в нем источник постоянного напряжения Vs=1 мВ и резисторы Rs=1 кОм, Ri=1,1 кОм, R0=40 кОм и RL=10 кОм. Поскольку выходной ток F определяет ток базы Ib, входные полюса подключены последовательно с резисторами Rs и Ri и выходными полюсами источника Е, входные полюса компонента Е должны быть подключены параллельно резистору R0, как и показано на схеме (рис. 15.20). При этом нет необходимости использовать V0, как на рис. 3.7, поскольку эту роль выполняют выходные полюса источника Е. Установим следующие значения коэффициентов усиления: F=50 (для hfe) и Е=2,5Е-4 (для hre). Пронумеруйте узлы и подготовьте конфигурацию моделирования, используя имя hparmods и запросив анализ для получения параметров смещения. Должны быть установлены опции анализа .OP и «Calculate small-signal DC gain (.TF).» Используйте для входного источника имя Vs и для выходной переменной величину V(4).  Рис. 15.20. Модель в h-параметрах для биполярного транзистора BJT Выполните моделирование и проверьте отсутствие ошибок. Если их нет, закройте выходной файл и используйте Word, чтобы распечатать сокращенную версию этого файла, как показано на рис. 15.21. Сравните ваши результаты с показанными на рис. 3.8. Полученные значения должны быть теми же, но нумерация узлов должна отличаться. Обратите внимание, что путем включения «проверки» с помощью команды .TF мы получили V(4)/V_Vs=-2,000Е+02 и входное сопротивление относительно V_Vs равным 2,0000Е+03 и выходное сопротивление относительно V(4) равным 8.400Е+03. Мы снова убеждаемся, что при использовании PSpice, как в главе 3, для анализа потребовалось значительно меньше времени, чем для анализа в Capture, при котором схема моделировалась более громоздким способом. **** 10/02/99 20:25:15 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: hparmods *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .OP .TF V([4]) V_Vs .PROBE *Netlist File: .INC "hparmod-SCHEMATIС1.net" *Alias File: **** INCLUDING hparmod-SCHEMATIC1.net **** * source HPARMOD F_F 4 0 VF_F 50 VF_F 3 5 0V E_E 5 0 4 0 2.5E-4 R_RL 4 0 10k R_Ro 4 0 40k R_Ri 2 3 1.1k R_Rs 1 2 1k V_Vs 1 0 1mV **** RESUMING hparmod-SCHEMATIC1-hpamods.sim.cir **** .INC "hparmod-SCHEMATIC1.als" INCLUDING hparmod-SCHEMATIC1.als **** .ALIASES F_F F(3=4 4=0 ) VF_F F(1=3 2=5 ) E_E E(3=5 4=0 1=4 2=0 ) R_RL RL(1=4 2=0 ) R_Ro Ro(1=4 2=0 ) R_Ri Ri(1=2 2=3 ) R_Rs Rs(1=1 2=2 ) V_Vs Vs(+=l -=0 ) _ _(1=1) _ _(2=2) _ _(3=3) _ _(4=4) _ _(5=5) .ENDALIASES **** RESUMING hparmod-SCHEMATIC1-hparmods.sim.cir **** .END **** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) .0010 ( 2) 500.0Е-06 ( 3) -50.00E-06 ( 4) -.2000 ( 5) -50.00E-06 VOLTAGE SOURCE CURRENTS NAME CURRENT VF_F 5.000E-07 V_Vs -5.000E-07 TOTAL POWER DISSIPATION 5.00E-10 WATTS **** VOLTAGE-CONTROLLED VOLTAGE SOURCES NAME E_E V-SOURCE -5.000E-05 I-SOURCE 5.000E-07 **** CURRENT-CONTROLLED CURRENT SOURCES NAME F_F I-SOURCE 2.500E-05 **** SMALL-SIGNAL CHARACTERISTICS V(4)/V_Vs = -2.000E+02 INPUT RESISTANCE AT V_Vs = 2.000E+03 OUTPUT RESISTANCE AT V(4) = 8.400E+03 Рис. 15.21. Выходной файл для модели в h-параметрах Упражнение по созданию графической схемы было, однако, поучительно, и анализ заслуживает внимания, по крайней мере, с этой точки зрения. Обратите внимание на строку файла псевдонимов для зависимого источника E_E: E_E 5 0 4 0 2.5Е- 4 Первые два полюса (5, 0) — выходные полюсы, показывают расположение зависимого источника в схеме, в то время как входные полюсы (4, 0) указывают на управляющее напряжение (от которого зависит E) снимаемое с R0. Зависимый источник F_F описан как F_F 4 0 VF_F 50 Первые два полюса (4, 0) являются выходными полюсами, показывающими, где вводится в схему ток F. Входные полюсы включены в контур последовательно с компонентами, через которые проходит независимый ток (управляющий источником F). В команде F_F эта управляющая цепь показана именем источника напряжения в контуре. Контур, через который проходит ток Ib, включает также и напряжение Е, что ясно видно из схемы. В перечне элементов (netlist) имеется команда ввода VF_F 3 5 0V Эта строка была сформирована программой, чтобы ввести в листинг источник И), который был необходим в схеме на рис. 3.7 вместе с листингом F, который использовался в PSpice. Не забудьте, что наши результаты можно при желании представить в действующих значениях для переменных составляющих, и обратите внимание на следующее: ток через источник напряжения VF_F равен 5.000Е-07 А. Это ток базы. С помощью других известных значений это легко проверить:  Источники напряжения, управляемые напряжением, обозначенные на рис. 15.21 как V-SOURCE, задают напряжение на узле 3, равное -50 мкВ, а компонент I-SOURCE создает ток в выходном контуре F. Поскольку коэффициент усиления источника F равен 50, ток F=50Ib=25 мА. После деления между двумя сопротивлениями ток через RL равен (0,8·25)мкА=20 мкА. На рисунке этот ток направлен вверх, что нужно показать также и на вашей схеме. Напряжение на узле 4 равно (-20 мкА)(10 кОм)=0,2 В, что подтверждает значение, приведенное в выходном файле. Это отрицательное выходное напряжение, инвертированное относительно напряжения Vs. Характеристики полевых транзисторовДемонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис. 15.22). Номинальные значения для VGS и VDD показаны на рисунке. Определите опции моделирования в Simulation Profile, используя имя jfetchs. Внутренний цикл вариации использует значения источника напряжения VDD от 0 до 12 В с шагом в 0,2 В. Внешний цикл определяется изменением напряжения VGS от 0 до 4 В с шагом в 1 В.  Рис. 15.22. Схема смещения для n-канального полевого транзистора Выполните моделирование и получите в Probe график ID(J1). Вы должны получить семейство кривых с параметром VGS, приведенных на рис. 15.23. Кривые показывают, что наибольшие токи соответствуют VGS=0. Ниже расположена кривая с параметром VGS=–1 В и так далее. Напряжением отсечки является VGS=–3 В.  Рис. 15.23. Ток стока в n-канальном полевом транзисторе Выходной файл включает параметры модели J2N3S19: пороговое напряжение (отсечки) VTO=-3 В, коэффициент передачи BETA и другие. Они отражены на рис. 15.24. В приложении D приведены все параметры модели для J (JFET). **** 10/03/99 11:45:33 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: jfetchs *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .DC LIN V VDD 0V 12V 0.2V + LIN V_VGS 0V 4V 1V .PROBE *Netlist File: .INC "jfetch-SCHEMATIC1.net" *Alias File: **** INCLUDING jfetch-SCHEMATIC1.net **** * source JFETCH J_J1 2 1 0 J2N3819 V_VDD 2 0 12V V_VGS 0 1 1V **** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir **** .INC "jfetch-SCHEMATIC1.als" **** INCLUDING jfetch-SCHEMATIC1.als **** .ALIASES J_J1 J1(d=2 g=1 s=0 ) V_VDD VDD(+=2 -=0 ) V_VGS VGS(+=0 -=1 ) _ _(1=1) _ _(2=2) .ENDALIASES .END **** Junction FET MODEL PARAMETERS J2N3819 NJF VTO -3 BETA 1.304000E-03 LAMBDA 2.250000E-03 IS 33.570000E-15 ISR 322.400000E-15 ALPHA 311.700000E-06 VK 243.6 RD 1 RS 1 CGD 1.600000E-12 CGS 2.414000E-12 M .3622 VTOTC -2.500000E-03 BETATCE -.5 KF 9.882000E-18 Рис. 15.24. Выходной файл для n-канального полевого транзистора Хотя предыдущие выпуски программного обеспечения от MicroSim использовали для создания рисунков программу Schematics вместо Capture, автоматически формируя команду .ОР в схемном файле, используемая в книге версия Capture этого не делает. Следовательно, значения параметров смещения не выводятся в выходном файле. Чтобы получить эти значения, отредактируете параметры настройки моделирования и запросите анализ параметров смещения путем проверки с опцией .OP. Выходной файл при таком запуске показан на рис. 15.25. Информация, дублирующая информацию предыдущего выходного файла, из него удалена. Убедитесь, что выходной файл соответствует графику, показывая VDD=12 В, VGS=–1 В, IDD=5,328 мА. **** 10/03/99 12:27:36 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: jfetchs *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .OP .PROBE *Netlist File: .INC "jfetch-SCHEMATIC1.net" *Alias File: **** INCLUDING jfetch-SCHEMATIC1.net **** * source JFETCH J_J1 2 10 J2N3819 V_VDD 2 0 12V V_VGS 0 1 1V **** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir **** .INC "jfetch-SCHEMATIC1.als" **** INCLUDING jfetch-SCHEMATIC1.als **** .ALIASES J_J1 J1(d=2 g=1 s=0 ) V_VDD VDD(+=2 -=0) V_VGS VGS(+=0 -=1 ) _ _(1=1) _ _(2=2) .ENDALIASES **** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir **** .END **** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) -1.0000 ( 2) 12.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_VDD -5.328E-03 V_VGS -1.321E-12 TOTAL POWER DISSIPATION 6.39E-02 WATTS **** JFETS NAME J_J1 MODEL J2N3819 ID 5.33E-03 VGS -1.00E+00 VDS 1.20E+01 GM 5.34E-03 GDS 1.17E-05 CGS 1.83E-12 CGD 6.15E-13 Рис. 15.25. Выходной файл, использующий опцию .OР Усилители на полевых транзисторахВ схеме усилителя на полевом транзисторе, приведенной на рис. 11.7, использовалась встроенная модель транзистора. Как говорилось в этом примере, строки, описывающие такое устройство, могли бы иметь вид: JFET 3 1 2 JM .MODEL JM NJF (RD=10 RS=10 VTO=3V BETA=0.2m) Эти строки вводят универсальный встроенный полевой транзистор JFET, для которого мы выбрали имя JM. Если мы создаем эту схему с помощью Capture, мы не можем просто выбрать компонент JFET; вместо этого мы должны выбрать один из доступных компонентов с конкретным именем. Затем можно изменить параметры модели так, чтобы она удовлетворяла нашим требованиям. Начните новый проект с именем Jfetampl и введите схему, показанную в рис. 11.7, используя компоненты VAC (для Vi), C (для Сb и Cs), R (для Rg, Rd и Rs), J2N3819 (для полевого транзистора) и VDC (для VDD). Задайте значения компонентов, которые использовались ранее. Схема, которую вы должны получить, показана на рис. 15.26. Полевой транзистор, используемый на рис. 11.7, описывается в PSpice командой .MODEL JM NJF (RD=10 RS = 10 VTO=-3V BETA=0.2m)  Рис. 15.26. Усилитель на полевом транзисторе Отредактируем модель конкретного транзистора J2N3819 так, чтобы она соответствовала этой команде. Выберите JFET, щелкнув на его символе, затем выберите Edit, PSpice Model. При этом на экране появится окно OrCAD Model Editor, в котором могут быть сделаны изменения. Задайте «Beta=0.2 m», «Rd=10» и «Rs=10», как показано на рис. 15.27. Сохраните эти изменения и закройте окно редактора модели.  Рис. 15.27. Изменение параметров транзистора JFET в программе Model Editor Сохраните схему и подготовьте новую конфигурацию моделирования на PSpice с именем jfetamps. Анализ должен быть проведен при линейной вариации частоты от 4900 до 5100 Гц, используя 201 точку. Выполните анализ, и в Probe проверьте значения следующих величин при f=5 кГц: I(Rd)=0,876 мкА; V(1)=1 мВ; V(3)=7,73 мВ и V(2)=1,8 мкВ. Отметим, что различные напряжения могут также быть отображены при использовании записей типа V(Cb:2), V(Rd:1), V(Rs:1) и т.п. Вообще предпочтительно пронумеровать предварительно узлы и обращаться затем к напряжениям с номерами узлов. Таким образом, в этом примере V(3) представляет собой напряжение на стоке JFET относительно земли. Нумерация узлов задается также командой псевдонимов выходного файла: J_J J1(d=3 g=1 s=2) что еще проще понять. Если вы забудете перенумеровать узлы, вы будете иметь дело с громоздкими обозначениями автоматической нумерации типа N00034. В выходном файле на рис. 15.28 показан список измененных параметров J2N3819. Значение VТО=–3 не было изменено, но Beta, Rd и Rs были заменены приведенными значениями. Выходной файл, приведенный на рис. 15.29, показывает компоненты схемы, значения параметров и напряжения смещения для VDD=18 В. Выходной файл может содержать следующие инструкции: WARNING-Unable to find index file (JFETAMPL.ind) for library file JFETAM + PL.lib WARNING-Making new index file (JFETAMPL.ind) for library file JFETAMPL.lib Index has 1 entries from 1 file(s). (ПРЕДУПРЕЖДЕНИЕ — Невозможно найти индексный файл (JFETAMPL.IND) для библиотечного файла JFETAM + PL.LIB ПРЕДУПРЕЖДЕНИЕ — Создайте новый индексный файл (JFETAMPL.IND) для библиотечного файла JFETAMPL.LIB Индекс имеет 1 вход из 1 файла(ов).)  Рис. 15.28. Схема JFET и изменение выходного файла **** 10/03/99 14:20:08 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profiles jfetamps *Libraries: * Local Libraries : .LIB ".\jfetampl.lib" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .AC LIN 201 4900Hz 5100Hz .PROBE *Netlist File: .INC "jfetampl-SCHEMATIC1.net" *Alias Files **** INCLUDING jfetampl-SCHEMATIC1.net **** * source JFETAMPL V_VDD 4 0 18V R_Rs 2 0 770 R_Rg 1 0 0.5MEG R_Rd 3 4 8.8k С_Cs 2 0 15uF С_Cb 1A 1 15uF J_J1 3 1 2 J2N3819 V_V1 1A 0 DC 0V AC 1mV 0 **** RESUMING jfetampl-SCHEMATIC1-jfetamps.sim.cir **** .INC "jfetampl-SCHEMATIC1.als" **** INCLUDING jfetampl-SCHEMATIC1.als **** .ALIASES V_VDD VDD(+=4 -=0 ) R_Rs Rs(1=2 2=0 ) R_Rg Rg(1=1 2=0 ) R_Rd Rd(1=3 2=4 ) C_Cs Cs(1=2 2=0 ) C_Cb Cb(1=1A 2=1 ) J_J1 J1(d=3 g=1 s=2 ) V_V1 V1(+=1A -=0 ) .ENDALIASES .END **** Junction FET MODEL PARAMETERS J2N3839 NJF VTO -3 BETA 200.000000E-06 LAMBDA 2.250000E-03 IS 33.570000E-15 ISR 322.400000E-15 ALPHA 311.700000Е-06 VK 243.6 RD 10 RS 10 BETATCE -.5 KF 9.882000E-18 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 605.8E-09 ( 2) .7719 ( 3) 9.1779 ( 4) 18.0000 ( 1A) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_VDD -1.003E-03 V_V1 0.000E+00 TOTAL POWER DISSIPATION 1.80E-02 WATTS Рис. 15.29. Выходной файл усилителя на JFET-транзисторе Эти предупреждения служат напоминанием, что до выполнения анализа библиотечный файл jfetampl.lib отсутствует. Он будет создан после выполнения анализа наряду с файлом jfetampl.ind. Новый библиотечный файл находится в вашем каталоге SPICE и содержит исходные данные, показанные на рис. 15.27. Листинг идентичен существующему в eval.lib, за исключением параметров Beta, Rd и Rs, которые мы изменили. Новая модель называется локальной моделью и доступна для использования только со схемой jfetampl. Анализ переходных процессов (временные диаграммы для JFET)Чтобы наблюдать временные диаграммы JFET и сравнивать наши результаты с показанными на рис. 11.8, необходимо заменить тип источника Vs, выбрав VSIN вместо VAC. Сделайте это и задайте следующие значения для нового источника: напряжение смещения равно 0, f=5 кГц и амплитуда напряжения равна 1 мВ. Выберите PSpice, New Simulation Profile с именем jfetamp2. Проведите анализ переходного процесса до 600 мкс с максимальным размером шага в 0,6 мкс. Проведите моделирование и в Probe получите напряжение стока v(3) и напряжение на управляющем электроде v(1), как показано на рис. 15.30. Убедитесь, что максимальное значение напряжения на стоке составляет 9,1857 В, а минимальное значение — 9,1702 В. Это дает значение для двойной амплитуды 15,5 мВ или амплитуду 7,75 мВ, что, по существу, совпадает с данными на рис. 11.8.  Рис. 15.30. Напряжения на стоке и управляющем электроде усилителя на JFET Анализ частотных характеристик биполярного транзистораКомпонент PSpice Q2N3904 имеет характеристики, близкие к характеристикам реального транзистора. Обратимся к рис. D.5, на котором показана модель BJT. Мы хотим исследовать высокочастотную реакцию транзистора. Начните новый проект в Capture с именем hifreq. Введите схему, показанную на рис. 15.31, которая основана на схеме на рис. 10.13 (исключен только резистивный датчик тока RB). Мы не пытались сохранить первоначальную нумерацию узлов. Используйте компонент VAC для Vs, установив для него значение напряжения в 1 мВ. Значения R и С показаны на рисунке. Сначала мы не будем изменять параметры транзистора, а затем значение hFE будет изменено, как в главе 10.  Рис. 15.31. Схема усилителя на биполярном транзисторе на высоких частотах Закончив схему, сохраните ее и подготовьте моделирование на PSpice с именем hifreqs. Используйте вариацию частоты от 100 кГц до 100 МГц с шагом в 50 точек на декаду. Проведите анализ и получите график выходного напряжения на коллекторе V(5). Убедитесь, что выходное напряжение при частоте f=100 кГц составляет 9,123 мВ. Таким образом, коэффициент усиления на средних частотах с источника на коллектор равен 9,123. Это значение будет использоваться при установлении верхней частоты снижения на 3 дБ. Удалите этот график и получите график 20·lg(V(5)/9,123mV). Он показан на рис. 15.32 вместе со схемой. Используйте курсор, чтобы проверить, что верхняя частота снижения на 3 дБ равна f=37,15 МГц.  Рис. 15.32. Частотная характеристика для биполярного транзистора Изменение характеристик транзистораВ примере на рис. 10.13 коэффициент усиления BF-транзистора был установлен в команде описания модели: .MODEL BJT NPN(BF=80) Изменим в Capture это значение, возвратившись к схеме и выделив транзистор. Из главного меню выберем Edit, PSpice model. Когда на экране появится OrCAD Model Editor, измените значение Bf с 416,4 на 80. Сохраните его и выйдите из редактора модели. Снова выполните анализ на PSpice. Нет необходимости изменять тип анализа или значения частоты. В Probe получите значение V(5) при f=100 кГц. Оно должно составлять 8,803 мВ. Теперь получим график 20·lg(V(5)/8,803 mV). Используйте курсор, чтобы найти частоту снижения на 3 дБ, которая должна теперь составлять f=40 МГц. Пожертвовав коэффициентом усиления, мы повысили частоту снижения на 3 дБ, расширив полосу пропускания. Примечания:9 Лучше всего найти этот файл системой поиска, имеющейся в Windows. Для этого достаточно в графе «Файлы и папки» набрать Capture, и из появившегося списка выбрать Capture\library. (Примеч. переводчика). |

|

||

|

Главная | В избранное | Наш E-MAIL | Добавить материал | Нашёл ошибку | Наверх |

||||

|

|

||||