|

||||

|

|

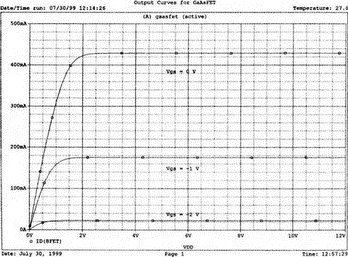

11. Полевые транзисторыВстроенные модели для полевых транзисторов (FET) обозначены в PSpice именами, начинающимися: с J для канальных полевых транзисторов (JFET), с М для МОП-транзисторов (MOSFET) и с В для арсенид-галлиевых транзисторов (GaAsFET). Перед использованием любого из этих приборов желательно получить наборы характеристик, позволяющие правильно определить напряжения и токи покоя. Выходные характеристики полевых транзисторовДемонстрационная версия PSpice содержит модели для двух типов n-канальных полевых транзисторов (JFET) в библиотеке EVAL.LIB. Получим необходимый набор выходных характеристик для транзистора J2N3819. Входной файл для анализа схемы рис. 11.1 содержит следующие команды: Output Characteristics for JFET J2N3819 VGS 1 0 0V VDD 2 0 12V JFET 2 10 J2M3819 .DC VDD 0 12V 0.2V VGS 0 -4V 1V .PROBE .LIB EVAL.LIB .END  Рис. 11.1. Схема для снятия характеристик полевых транзисторов JFET Вложенный цикл команды .DC позволяет получить пять характеристик при целочисленных значениях VGS от 0 до -4 В. Однако после выполнения анализа вы обнаружите только четыре характеристики (рис. 11.2). Так как верхний график соответствует V  Рис. 11.2. Выходные характеристики транзисторов JFET Входные характеристики усилителя на полевых транзисторахПри получении входных характеристик величина VGS используется во внешнем цикле команды .DC в качестве основной переменной, откладываемой по оси X. Значения VDD изменяются от от 2 до 10 В с шагом в 4 В, создавая три характеристики. Нижняя характеристика соответствует VDD=2 В. Для последующего использования полезно маркировать характеристики. Входной файл для анализа Input Characteristics for JFET VGS 1 0 0V VDD 2 1 10V JFET 2 10 J2N3819 .DC VGS -3 0 0.05V VDD 2 V 10V 4V .PROBE .LIB EVAL.LIB .END Характеристики с соответствующими метками показаны на рис. 11.3.  Рис. 11.3. Входные характеристики транзисторов JFET Библиотека рабочей версии содержит только n-канальные JFET. Если вам необходим p-канальный JFET, то вы может вставить команду .MODEL во входной файл или изменить библиотеку EVAL.LIB, чтобы включить одно или большее количество таких устройств. Ввод модели для J2N3819 осуществляется следующим образом: .model J2N3819 NJF (Beta=1.304m Betatce=-.5 Rd=1 Rs=1 Lambda=2.25m +Vto=-3 +Vtotc=-2.5m Is=33.57f Isr=322.4f N=1 Nr=2 Xti = 3 Alpha = 311.7 +Vk=243.6 Cgd=1.6p M=.3622 pb=1 Fc=.5 Cgs=2.414p Kf=9.882E-18 +Af=1) National pid=50 case=T092 88-08-01 rmn BVmin=25 Обратите внимание, что для порогового напряжения задано значение Vt0=-3 В. Когда используется р-канальный JFET, модель должна быть PJF (а не NJF) и должно использоваться положительное значение Vt0. Токи смещения полевых транзисторовСхема с автоматическим смещением приведена на рис. 11.4. Во встроенной модели для n-канального JFET значения, заданные по умолчанию для ряда параметров, изменены. Новые значения показаны в следующем входном файле: n-Channel JFET Bias Circuit VDD 4 0 18V RG 1 0 0.5MEG RS 2 0 770 RD 4 3 8.8k JFET 3 1 2 JM .MODEL JM NJF(RD=10 RS=10 VTO=-3 BETA=0.2m) .DC VDD 18V 18V 18V .OP .OPT nopage .PRINT DC I(RD) I(RS) I(RG) .END  Рис. 11.4. Схема с автоматическим смещением транзистора JFET Выходной файл приведен на рис. 11.5. Чтобы посмотреть, совпадают ли результаты стандартного схемотехнического расчета и анализа на PSpice, необходимо найти значение IDSS. Выполните анализ, подобный показанному на рис. 11.2, и убедитесь, что для этого JFET IDSS=1,78 мА. Сравните ваши результаты с рис. 11.6. Воспользовавшись этим значением, найдем  **** 07/29/99 11:29:21 *********** Evaluation PSpice (Nov 1998) ************** n-Channel JFET Bias Circuit VDD 4 0 18V RG 1 0 0.5MEG RS 2 0 770 RD 4 3 8.8k JFET 3 1 2 JM .MODEL JM NJF(RD=10 RS=10 VTO=-3 BETA=0.2m) .DC VDD 18V 18V 18V .OP .opt nopage .PRINT DC I(RD) I(RS) I(RG) .END **** Junction FET MODEL PARAMETERS JM NJF VTO -3 BETA 200.000000E-06 RD 10 RS 10 **** DC TRANSFER CURVES TEMPERATURE = 27.000 DEG С VDD I(RD) I(RS) I(RG) 1.800E+01 9.915E-04 9.915E-04 1.006E-11 **** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -9.915E-04 TOTAL POWER DISSIPATION 1.78E-02 WATTS **** JFETS NAME JFET MODEL JM ID 9.92E-04 VGS -7.63E-01 VDS 8.51E+00 GM 8.91E-04 GDS 0.00E+00 CGS 0.00Е+00 CGD 0.00Е+00 Рис. 11.5. Выходной файл с результатами анализа схемы на рис. 11.4  Рис. 11.6 Выходные характеристики схемы на рис. 11.4 Используем теперь значение IDSS, полученное в PSpice, чтобы найти VGSS. В следующем уравнении IDSS представляет собой ток стока при насыщении:  Откуда при IDS=0,992 мА, IDSS=-1,78 мА и VP=3 В после преобразований получим VGS=0,78 В и затем  Значения VGS и gm согласуются с показанными на рис. 11.5. Усилители на полевых транзисторахМожно преобразовать схему смещения, показанную на рис. 11.4, в усилитель напряжения, добавив два конденсатора и источник переменного напряжения (рис. 11.7). Приведенный ниже входной файл предназначен для анализа на переменном токе при f=5 кГц: n-Channel JFET Amplifier circuit VDD 4 0 18V vi 1a 0 ac 1mV Cb 1a 1 15uF Cs 2 0 15uF RG 1 0 0.5MEG RS 2 0 770 RD 4 3 8.8k JFET 3 1 2 JM .MODEL JM NJF (RD=10 RS=10 VT0=-3V BETA=0.2m) .DC VDD 18V 18V 18V .OP .OPT nopage .PRINT DC I(RD) I(RS) I(RG) .ac lin 1 5kHz 5kHz .PRINT ac i(RD) v(3) v(1) v(2) .END  Рис. 11.7. Усилитель на транзисторе JFET Выходной файл показан на рис. 11.8. Просмотрите результаты анализа и убедитесь, что переменная составляющая напряжения на стоке V(3)=7,77 мВ, что дает коэффициент усиления по напряжению 7,77. Это близко к значению, получаемому из аппроксимирующего уравнения Av = gmRD = (0,891 мС) (8,8 кОм) = 7,8 **** 07/29/99 14:40:00 *********** Evaluation PSpice (Nov 1998) ************** n-Channel JFET Amplifier circuit VDD 4 0 18V vi 1a 0 ac 1mV Cb 1a 1 15uF Cs 2 0 15uF RG 1 0 0.5MEG RS 2 0 770 RD 4 3 8.8k JFET 3 1 2 JM .MODEL JM NJF(RD=10 RS=10 VTO=-3V BETA=0,2m) .DC VDD 18V 18V 18V .OP .OPT nopage .PRINT DC I(RD) I(RS) I(RG) .ac lin 1 5kHz 5kHz .PRINT ac i(RD) v(3) v(1) v(2) .END **** Junction FET MODEL PARAMETERS JM NJF VTO -3 BETA 200.000000E-06 RD 10 RS 10 VDD I(RD) I(RS) I(RG) 1.800E+01 9.915E-04 9.915E-04 1.006E-11 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000 ( 1a) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -9.915E-04 vi 0.000E+00 TOTAL POWER DISSIPATION 1.78E-02 WATTS **** JFETS NAME JFET MODEL JM ID 9.92E-04 VGS -7.63E-01 VDS 8.51E+00 GM 8.91E-04 GDS 0.00E+00 CGS 0.00E+00 CGD 0.00E+00 **** AC ANALYSIS TEMPERATURE = 27.000 DEG С FREQ I(RD) V(3) V(1) V(2) 5.000E+03 8.828E-07 7.768Е-03 1.000Е-03 1.873E-06 Рис. 11.8. Выходной файл с результатами анализа схемы на рис. 11.7 Временные диаграммы усилителейЧтобы получить временные диаграммы синусоидального входного напряжения и напряжения на стоке, необходимо несколько изменить входной файл. Входное напряжение задается синусоидальной функцией vi 1a 0 sin (0 1mV 5kHz) Анализ переходных процессов выполняется с помощью команды .TRAN 0.02ms 0.6ms которая при частоте 5 кГц предусматривает анализ на протяжении трех периодов колебаний. Проведите моделирование и по результатам в Probe убедитесь, что напряжение стока имеет максимальное значение 9,282 мВ и минимальное — 9,266 мВ. Это дает размах напряжения в 15,4 мВ и максимальное значение 7,7 мВ. Результаты близки к полученным ранее расчетным данным. Временные диаграммы показаны на рис. 11.9. Обратите внимание, что курсор расположен так, чтобы показать максимальное значение V(3). При этом входное напряжение находится в соответствующем минимуме.  Рис. 11.9. Временные диаграммы входного и выходного напряжений В выходном файле (рис. 11.10) показана модификация входного файла, позволяющая включить наряду с анализом переходных процессов еще и гармонический анализ для выходного напряжения V(3). Выходной файл показывает постоянную составляющую напряжения на истоке в 9,274 В. Вторая и более высокие гармоники имеют незначительную величину, давая общее гармоническое искажение менее 1%. n-Channel JFET Amplifier circuit VDD 4 0 18V vi 1a 0 sin(0 1mV 5kHz) Cb 1a 1 15uF Cs 2 0 15uF RG 1 0 0.5MEG RS 2 0 770 RD 4 3 8.8k JFET 3 1 2 JM .MODEL JM NJF(RD=10 RS=10 VTO=-3V BETA=0.2m) .DC VDD 16V 18V 18V .OP .OPT nopage nomod .TRAN 0.02ms 0.6ms .PROBE .FOUR 5kHz V(3) .END NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000 ( 1a) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -9.915E-04 vi 0.000E+00 TOTAL POWER DISSIPATION 1.78E-02 WATTS VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -9.915E-04 vi 0.000E+00 TOTAL POWER DISSIPATION 1.78E-02 WATTS **** FOURIER ANALYSIS TEMPERATURE = 27.000 DEG С FOURIER COMPONENTS OF TRANSIENT RESPONSE V(3) DC COMPONENT = 9.274381E+00 HARMONIC FREQUENCY FOURIER NORMALIZED PHASE NORMALIZED NO (HZ) COMPONENT COMPONENT (DEG) PHASE (DEG) 1 5.000E+03 7.679E-03 1.000E+00 -1.797E+02 0.000E+00 2 1.000E+04 2.155E-05 2.806E-03 -1.014E+02 7.829E+01 3 1.500E+04 2.311E-05 3.009E-03 -1.076E+02 7.208E+01 4 2.000E+04 2.231E-05 2.905E-03 -1.139E+02 6.578E+01 5 2.500E+04 2.154E-05 2.805E-03 -1.189Е+02 6.079E+01 6 3.000E+04 2.067E-05 2.692E-03 -1.247E+02 5.507E+01 7 3.500E+04 1.949E-05 2.538E-03 -1.300E+02 4.974E+01 8 4.000E+04 1.848E-05 2.406E-03 -1.352E+02 4.449E+01 9 4.500E+04 1.723E-05 2.244E-03 -1.399E+02 3.983E+01 TOTAL HARMONIC DISTORTION = 7.599231E-01 PERCENT Рис. 11.10. Выходной файл результатов анализа схемы на рис. 11.7, дополненный результатами спектрального анализа Мощные полевые транзисторы MOSFETДля изучения случая, касающегося МОП-транзисторов, необходимо выбрать соответствующую модель такого устройства из библиотеки EVAL.LIB. Это модель IRF150, которая отображает мощный МОП-транзистор n-типа. Чтобы познакомиться с его свойствами, рассмотрим семейства входных и выходных характеристик. Выходные характеристикиЧтобы получить выходные характеристики, используем схему, показанную на рис. 11.11. Входной файл для нее: n-Channel MOSFET Output Characteristics VDD 2 0 12V VGS 1 0 0VMFET 2 10 0 IRF150; сток, исток, затвор и подложка .DC VDD 0 12V 0.8V VGS 0 8V 1V .LIB EVAL.LIB .PROBE .END  Рис. 11.11. Схема для снятия характеристик МОП-транзисторов Как показано на рис. 11.11, источник и подложка объединены, как и требуется. Выходные характеристики показаны на рис. 11.12. В качестве примера больших токов стока отметим, что при VGS=5 В ток насыщения становится больше 7 А. Входной файл библиотечной модели для IRF150 задает пороговое значение напряжения при нулевом смещении Vt0=2,831 В. Для n-канального устройства это напряжение является положительным.  Рис. 11.12. Выходные характеристики МОП-транзистора Входные характеристикиДля входных характеристик несколько значений VDD будут использоваться, как показано в следующем файле: Input Characteristic for MOSFET VGS 1 0 0V VDD 2 0 10V MOS 2 10 0 IRF150 .DC VGS 0 8V 0.1V VDD 2V 10V 4V .PROBE .LIB EVAL.LIB .END Полученный в результате график показан на рис. 11.13. Из него видно, что пороговое значение VGS немного ниже 3 В и что характеристики при VDD=6 В или больше сливаются в одну кривую.  Рис. 11.13. Входные характеристики МОП-транзистора Усилители на MOSFETУсилитель мощности, использующий IRF150, показан на рис. 11.14. Так как используется режим с большими токами истока и стока, значения Rd и Rs составляют 2 и 0,5 Ом соответственно. Резисторы R1 и R2 образуют делитель напряжения, обеспечивающий значение VGS=4,7 В. При этом входной файл имеет вид: n-Channel Power MOSFET Amplifier VDD 4 0 18V vi 1 0 ac 0.5V R1 4 2 330k R2 2 0 220k Rd 4 3 2 Rs 5 0 0.5 Cb 1 2 15uF Cs 5 0 15uF MFET 3 2 5 5 IRF150 .DC VDD 12V 12V 12V .OP .OPT nopage .PRINT DC I(RD) I(R1) I(R2) I(RS) .ac Lin 1 5kHz 5kHz .PRINT ac i (Rd) v(2) v(3) .LIB EVAL.LIB .END  Рис. 11.14. Усилитель мощности на МОП-транзисторе Выходной файл показан на рис. 11.15. Приведены постоянные и переменные составляющие. Среди постоянных составляющих показаны ток стока (и истока) ID=1,781 А, напряжения на стоке V(3)=7,827 В и на истоке V(5)=2,543 В. n-Channel Power MOSFET Amplifier VDD 4 0 18V vi 1 0 ac 0,5V R1 4 2 330k R2 2 0 220k Rd 4 3 2 Re 5 0 0.5 Cb 1 2 15uF Cs 5 0 15wF MFET 3 2 5 5 IRF150 .DC VDD 12V 12V 12V .OP .OPT nopage .PRINT DC I(RD) I(R1) I(R2) I(Re) .ac lin 1 5kHz 5kHz .PRINT ac i(Rd) v(2) v(3) .LIB EVAL.LIB .END **** MOSFET MODEL PARAMETERS IRF150 NMOS LEVEL 3 L 2.000000E-06 W .3 VTO 2.831 KP 20.530000E-06 GAMMA 0 PHI .6 LAMBDA 0 RD 1.031000E-03 RS 1.624000E-03 RG 13.89 RDS 444.400000E+03 VDD I(RD) I(R1) I(R2) I(Rs) 1.200E+01 1.781E+00 2.182E-05 2.182E-05 1.781E+00 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 7.2000 ( 3) 7.8271 ( 4) 18.0000 ( 5) 2.5432 VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -5.086E+00 vi 0.0000+00 TOTAL POWER DISSIPATION 9.16E+01 WATTS **** MOSFETS NAME MFET MODEL IRF150 ID 5.09E+00 VGS 4.66E+00 VDS 5.28EE+00 VBS 0.00E+00 VTH 2.83E+00 VDSAT 1.82E+00 GM 5.60E+00 **** AC ANALYSIS TEMPERATURE = 27.000 DEG С FREQ I(Rd) V(2) V(3) 5.000E+03 7.536E-01 4.9998-01 1.507E+00 Рис. 11.5. Выходной файл с результатами анализа схемы на рис. 11.4 Анализ переменных составляющих дает входное напряжение vi=0,5 В и выходное напряжение на стоке v(3)=1,5 В, давая коэффициент усиления по напряжению, равный 3. Переменная составляющая выходного тока равна ID=0,7536А. Для всех переменных составляющих приведены максимальные значения. Временные диаграммыЧтобы получить временные диаграммы входного и выходного напряжений, необходимо слегка изменить входной файл. Как и в предыдущем примере, будет использовано синусоидальное входное напряжение: Vi 1 0 sin (0 0. 5V 5kHz) Наряду с анализом переходных процессов выполним и гармонический анализ. Проведем моделирование и используем Probe, чтобы получить графики v(3), i(Rd) и v(1). Результаты должны совпадать с приведенными на рис. 11.16. Используем режим курсора, чтобы найти максимальное значение выходного напряжения. Хотя значения каждого из максимумов слегка различаются из-за того, что график отражает переходной процесс, третий максимум равен 9,3188 В постоянная составляющая напряжения равна 7,8272 В. Для максимального значения переменной составляющей это дает значение 1,4916 В, которое близко к переменной составляющей, показанной в предыдущем анализе, и подтверждает коэффициент усиления по напряжению, равный 3.  Рис. 11.16. Входные и выходные сигналы для схемы на рис. 11.14 Изменения в схемном файле показаны в выходном файле (рис. 11.17). Обратите внимание, что выходное напряжение содержит небольшую вторую гармонику, общее гармоническое искажение слегка превышает 0,5%. Постоянная составляющая выходного напряжения равна 7,819 В, что лишь ненамного отличается от напряжения покоя для узла 3. n-Channel Power MOSFET Amplifier, Fourier analysis VDD 4 0 18V vi 1 0 sin(0 0.5V 5kHz) R1 4 2 330k R2 2 0 220k Rd 4 3 2 Rs 5 0 0.S Cb 1 2 15uF Cs 5 0 15uF MFET 3 2 5 5 IRF150 .DC VDD 12V 12V 12V .OP .OPT nopage nomod .TRAN 0.02ms 0.6ms .PROBE .FOUR 5kHz v(3) .LIB EVAL.LIB .END NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 7.2000 ( 3) 7.8271 ( 4) 18.0000 ( 5) 2.5432 VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -5.086E+00 vi 0.000E+00 TOTAL POWER DISSIPATION 9.16Е+01 WATTS **** INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG С VOLTAGE SOURCE CURRENTS NAME CURRENT VDD -5.086E+00 vi 0.000E+00 TOTAL POWER DISSIPATION 9.16Е+01 WATTS **** FOURIER ANALYSIS TEMPERATURE = 27.000 DEG С FOURIER COMPONENTS OF TRANSIENT RESPONSE V(3) DC COMPONENT = 7.819569E+00 HARMONIC FREQUENCY FOURIER NORMALIZED PHASE NORMALIZED NO (HZ) COMPONENT COMPONENT (DEG) PHASE (DEG) 1 5.000E+03 1.490E+00 1.000E+00 -1.703E+02 0.000E+00 2 1.000E+04 7.816E-03 5.246E-03 1.286E+02 2.989E+02 3 1.500E+04 3.212E-04 2.156E-04 -1.040E+02 6.630E+01 4 2.000E+04 1.882E-04 1.263E-04 -8.023E+01 9.005E+01 5 2.500E+04 1.502E-04 1.008E-04 -7.562E+01 9.465E+01 6 3.000E+04 1.972E-04 1.323E-04 -7.245E+01 9.782E+01 7 3.500E+04 1.758Е-04 1.180Е-04 -1.008E+02 6.944E+01 8 4.000E+04 4.582E-05 3.075E-05 -3.885E+01 1.314E+02 9 4.500E+04 1.703E-04 1.143Е-04 -3.659E+01 1.337E+02 TOTAL HARMONIC DISTORTION = 5.257215E-01 PERCENT Рис. 11.17. Выходной файл с результатами анализа схемы на рис. 11.14, включая гармонический анализ Арсенид-галлиевые полевые транзисторыPSpice включает встроенную модель для арсенид-галлиевого n-канального транзистора (GaAsFET). Имя этого прибора начинается с В. Хотя библиотека демонстрационной версии не содержит никаких входных файлов для этих транзисторов, вы можете определять параметры модели или просто использовать значения по умолчанию, приведенные в приложении D. Значение по умолчанию для напряжения отсечки Vto=–2,5 В. Пример типового входного файла, используемого для получения выходных характеристик, приведен ниже: Output Curves for GaAsFET VOD 2 0 12V VGS 1 0 0V BFET 2 1 0 B1; узлы стока, затвора и истока .MODEL B1 GAsFET (Vto=-2.5 B=0.3 Rg=1 Rd=1 Rs=1 Vbi=0.5V) .DC VDD 0 12V 0.2V VGS 0 -3V 1V .PROBE .END Выполните моделирование на PSpice, затем используйте Probe, чтобы получить графики ID(BFET), приведенные на рис. 11.18. Убедитесь, что IDSS=429 мА.  Рис. 11.18. Выходные характеристики арсенид-галлиевого транзистора ЗадачиОбратите внимание: в PSpice параметр BETA для JFET определяется как  11.1. Определите с помощью PSpice ток стока ID и напряжение на стоке VDS для схемы с JFET-транзистором, показанной на рис. 11.19, при значениях VPO=2 В и IDSS=5 мА.  Рис. 11.19 11.2. Найдите значения точки покоя ID и VDS для схемы с JFET-транзистором, показанной на рис. 11.20. Транзистор имеет те же характеристики, что и в предыдущей задаче.  Рис. 11.20 11.3. В схеме на рис. 11.21 для МОП-транзистора со встроенным каналом найдите значения ID, VGS и VDS c помощью анализа на PSpice при IDSS=5 мА и VPO=2 B.  Рис. 11.21 11.4. В схеме полевого транзистора JFET, приведенной на рис. 11.22, IDSS=8 мА и VPO=5,0 В. В рабочей точке gd=0,3 мС. С помощью анализа на PSpice найдите коэффициент усиления по напряжению v0|vi для низких частот.  Рис. 11.22 11.5. Усилитель на базе транзистора JFET показан на рис. 11.23. Заданы значения rd=100 кОм и gm=2850 мкС. Используйте PSpice, чтобы найти коэффициент усиления по напряжению v0|vs.  Рис. 11.23 11.6. Параметры усилителя на МОП-транзисторе, показанного на рис. 11.24: VT=2,5 В, (β=0,6 А/В² и rd=120 кОм. Используйте PSpice, чтобы найти коэффициент усиления по напряжению v0|vs.  Рис. 11.24 11.7. Схема прерывателя показана на рис. 11.25. На вход схемы включен источник синусоидального напряжения vi с частотой 1 кГц и амплитудой, меньшей чем VРO. Управляющее напряжение vg имеет прямоугольную форму при частоте 2 кГц. Используйте анализ на PSpice/Probe, чтобы получить выходное напряжение v0.  Рис. 11.25 |

|

||

|

Главная | В избранное | Наш E-MAIL | Добавить материал | Нашёл ошибку | Наверх |

||||

|

|

||||